恒温晶振 (OCXO)

恒温晶振 (OCXO)

温补晶振 (TCXO)

温补晶振 (TCXO)

压控晶振 (VCXO)

压控晶振 (VCXO)

晶体振荡器 (XO)

晶体振荡器 (XO)

晶体谐振器(Crystal)

晶体谐振器(Crystal)

晶体滤波器(Crystal Filters)

晶体滤波器(Crystal Filters)

LC滤波器模块(LC Filter)

LC滤波器模块(LC Filter)

带阻滤波器(Bandstop Filter)

带阻滤波器(Bandstop Filter)

声表面波滤波器(SAW Filter)

声表面波滤波器(SAW Filter)

腔体滤波器(Cavity Filter)

腔体滤波器(Cavity Filter)

放大器(Amplifier)

放大器(Amplifier)

滤波器组模块(Filter Bank)

滤波器组模块(Filter Bank)

压控振荡器(VCO)

压控振荡器(VCO)

时钟模块 (Timing Module)

时钟模块 (Timing Module)

锁相介质振荡器(PLDRO)

锁相介质振荡器(PLDRO)

锁相环(PLL)

锁相环(PLL)

2017-3-29

2017-3-29

PECL和LVDS输出

什么是PECL和LVPECL?

•PECL代表“正发射极耦合逻辑电平”。 PECL是在高速时钟分配电路中常用的差分逻辑输出。 PECL需要+5 V电源。

•低电压PECL(LVPECL)代表设计用于3.3V或2.5V电源的PECL电路,电源电压与低压CMOS器件相同。

PECL输出的优点与缺点

• 优点:

- 由于电压摆幅大,抖动性能非常好。

- 适用于高速电路。

- 能够驱动长传输线。

• 缺点:

- 与单端输出相比,由于差分输出和外部直流偏置,功耗更大。

- 不兼容1.8V电源。

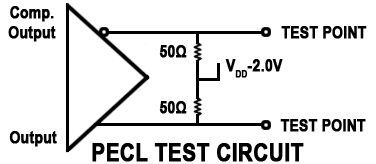

PECL端接电路 (推荐)

每个输出端接一个50Ω电阻到终端电压(Vdd - 2V)。

什么是LVDS输出?

•LVDS代表低电压差分信号,以1.2V的工作电压为中心,与电源无关。

•LVDS技术由ANSI / TIA / EIA-644行业标准定义。

•美国迪拉尼工程有限公司(DEI) 有许多晶体振荡器产品线,在3.3V和2.5V电源下具有LVDS输出选项。

LVDS输出的优点与缺点

• 优点:

- 与PECL输出相比,由于电压摆幅较小(通常约为350mV),功耗较低。

- 不易受噪声影响。

- 与CMOS / TTL相比,降低了EMI辐射。

• 缺点:

- 与PECL相比降低了抖动性能。

LVDS在哪里使用?

LVDS标准用于解决数据通信、电信、服务器、外设和计算机市场中需要高速数据传输的应用。

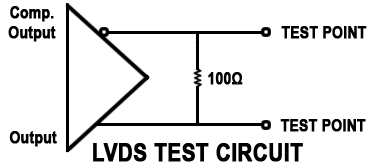

LVDS端接电路(推荐)

需要单个100Ω终端电阻。 一些接收器IC可能内部包含电阻器。

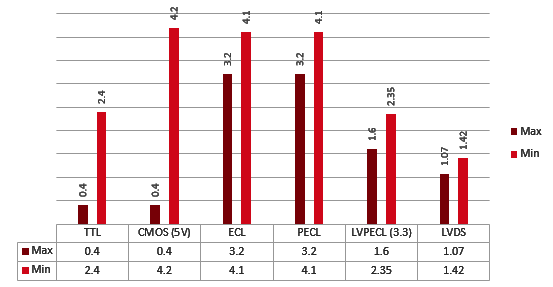

各种信号电平对比

关于我们 公司产品 产品应用 新闻公告 联系我们 English

友情链接: 恒温晶振

苏ICP备2022040084号-2 2016-2028迪拉尼 版权所有 技术支持:光芒网络keywords:恒温晶振 晶体振荡器 时钟模块 温补晶振 晶体滤波器 OCXO TCXO Crystal filter timing module crystal oscillator

扫描二维码关注微信公众号

您可以获得:

1.更高效的沟通体验

2.更快捷的报价通知

3.更方便的接询单体验